## Lösung: Protokollbeschreibungen in VHDL

Berechnen Sie die gesammte Transfer-Zeit (angenommen t1=200 ns, t2=300ns, t3=300 ns, t4=250 ns; Kanalverzögerung tk=100 ns).

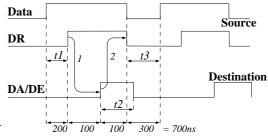

## 1 non-interlocked

Ereignisauslösung nur durch Laufzeitannahme  $\Longrightarrow$  non-interlocked

- 1. S: Daten sind gültig

- 2. D: Daten gelesen

Gesamtzeit: 650ns

$t_2$ : Zeit bis 'Destination' Datengültigkeit erkannt haben muss.

$t_3$ : Zeit bis 'Source' die Datenabnahme erkannt haben muß (DA  $\rightarrow$  0)

$t_4$ : Zeit bis 'Destination' spätestens das DA-Signal zurücknehmen muss (DA=0)

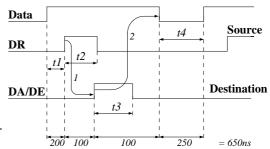

## 2 half-interlocked

Ereignisauslösung teilweise durch Laufzeitannahmen, Source setzt DR auf 0, wenn DA/DE=1 wird  $\Longrightarrow$  half-interlocked

- 1. S: Daten sind gültig

- 2. D: Daten gelesen

Zeitliche Annahme an DA durch  $t_2$

Gesamtzeit: 700ns

$t_2$ : Zeit bis 'Source' die Datenabnahme erkannt haben muss (DA  $\rightarrow$  0)

$t_3$ : Zeit bis 'Destination' spätestens das DA-Signal zurücknehmen muss (DA=0)

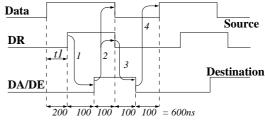

## 3 fully-interlocked

keine Zeitlichen Annahmen, Ereignisauslösung nur <br/>  $\underline{\textbf{Data}}$ durch Kommunikationspartner

$\Longrightarrow$  fully-interlocked

- 1. S: Daten sind gültig

- 2. D: Daten gelesen

- 3. S: OK. gebe Bus frei

- 4. D: OK. weitermachen

keine Zeitliche Annahmen Gesamtzeit: 600ns